Исследование просторов интернета показало, что SATA контроллера с полным исходным кодом для ПЛИС (FPGA), в виде недорогой железки, которая, при этом, еще и сразу работает, нет!

Пересмотрев на github.com весь ассортимент того, что с виду напоминает SATA host контроллер, я подобрал несколько проектов, представляющих интерес:

(1) https://github.com/CoreyChen922/sata_2_host_controller

(1.1) форк : https://github.com/danieltangdx/sata_2_host_controller

(2) https://github.com/freecores/sata_controller_core

(3) https://github.com/Siprj/sata-fpga

Первый проект под Virtex5 даже не собирается, так как не хватает файлов.

Проект по ссылке 1.1 содержит удаленный из первого проекта файл тестовой схемы system.mhs. С ним собирать пока не пробовал.

Второй исходник для Virtex6 под который есть отладочная плата. Плюс там есть довольно подробный тестовый проект с внутрисхемным анализатором ChipScope.

Теперь с этим набором вводных данных пробую разобраться. Сделал тестовые проекты с ChipScope отладкой под Virtex-6 плату и Wukong Artix-7 (от компании ChinaQMTECH). Они выложены в репозитории R.lab. Там, пока что, только вариант VHDL. Xilinx инструментарий ISE 14.7, так как поддерживаются старые микросхемы, которых уже нет в Vivado.

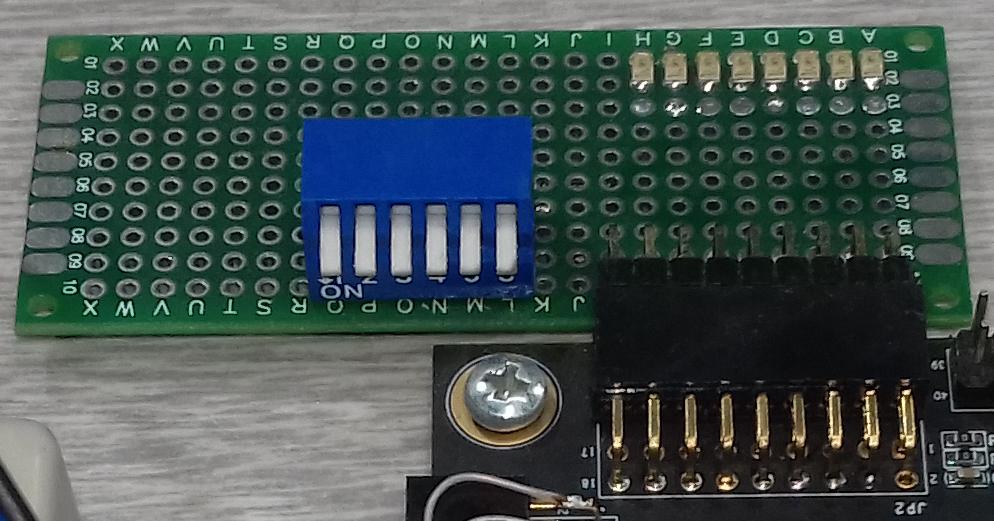

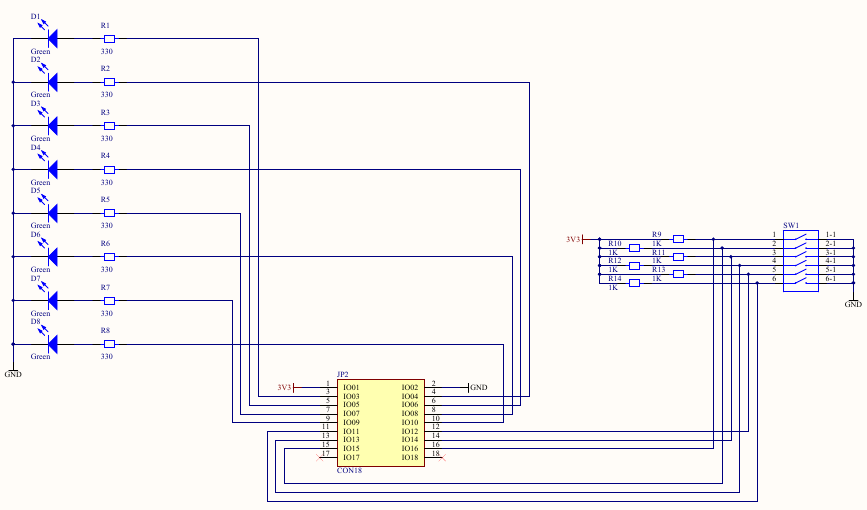

Сделал для платы Wukong дополнение со светодиодами и выключателями.

Схема дополнения выложена так же в репозитории с исходным файлом для Altium Designer.

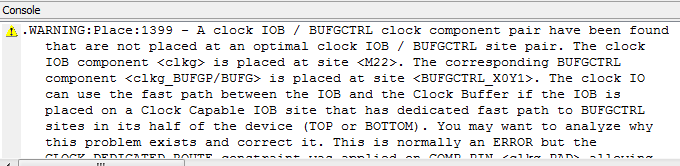

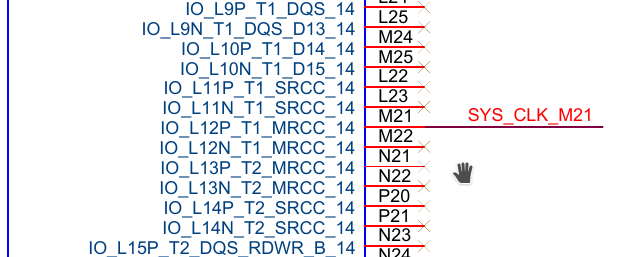

При сборке под плату Wukong выдается предупреждение про тактовый сигнал:

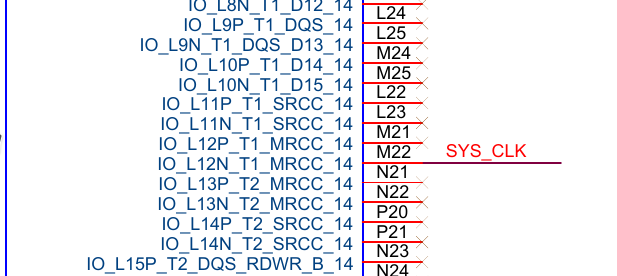

Оказалось, что это проблема с выбором тактового входа FPGA Artex-7 — они не все одинаковые. Описание проблемы чудом нашел в багрепортах репозитория ChinaQMTECH на гитхабе.

Проблема в том, что у Artex-7 есть ведущий и ведомые тактовые входы. Собираем для соседнего ведущего (номер входа) и все работает!

В имеющейся у меня версии платы тактовый сигнал подключен так:

А в новой версии Wukong платы, которая сейчас продается эта проблема уже исправлена.

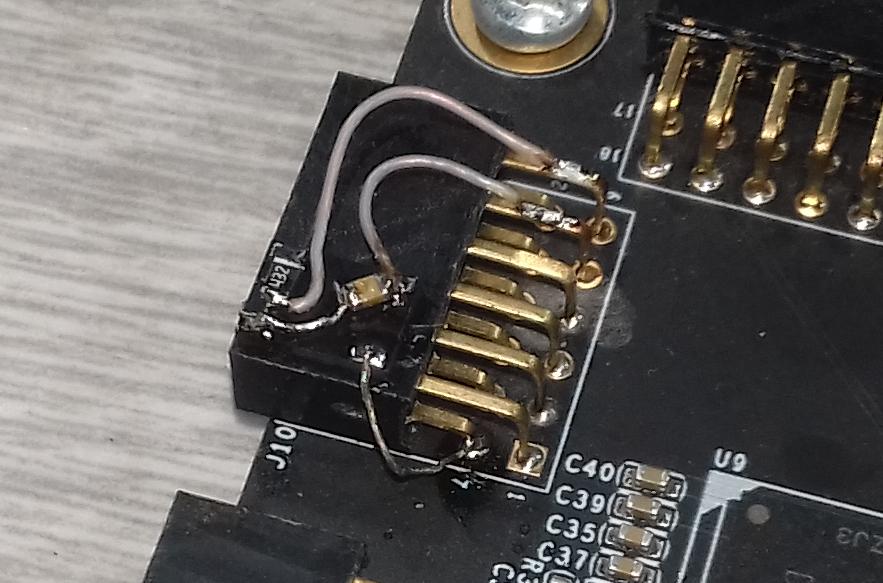

Но у меня плата старая. Решил припаять еще один генератор на 100 мегагерц к подходящему тактовому входу, выведенному на разъем расширения. Доработка выглядит так:

Пластиковый корпус кварца просто приклеил к разъему суперклеем. В разъеме J10 есть питание — подключился к нему. Провод на 7-ой контакт — это выход тактового сигнала.

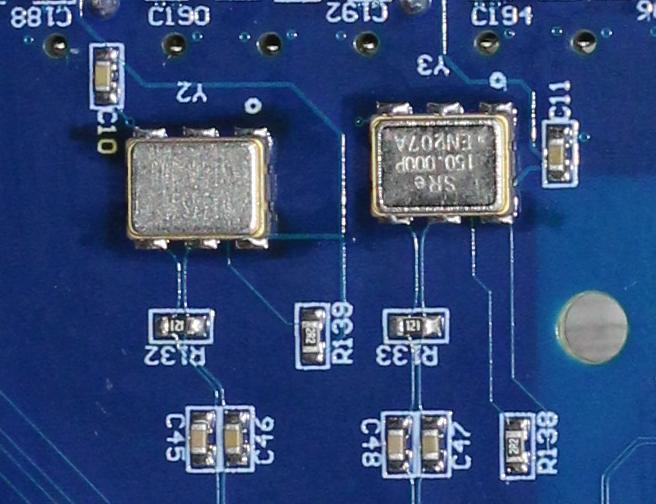

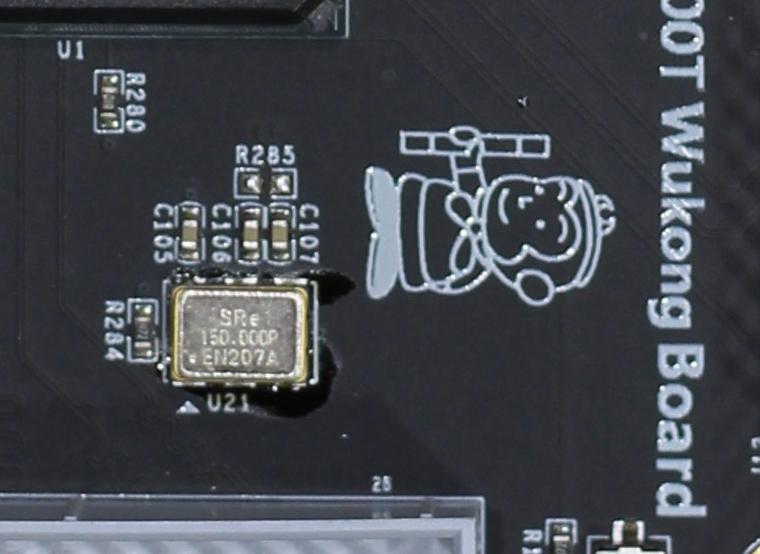

Для работы всех найденных исходных кодов SATA host контроллеров используется тактовый сигнал с частотой 150 мегагерц, подключенный к специальному входу для блока GTX. Следовательно, на всех платах перепаиваю соответствующий генератор на 150 мегагерц с дифференциальным выходом.

На плате Virtex6:

На плате Wukong:

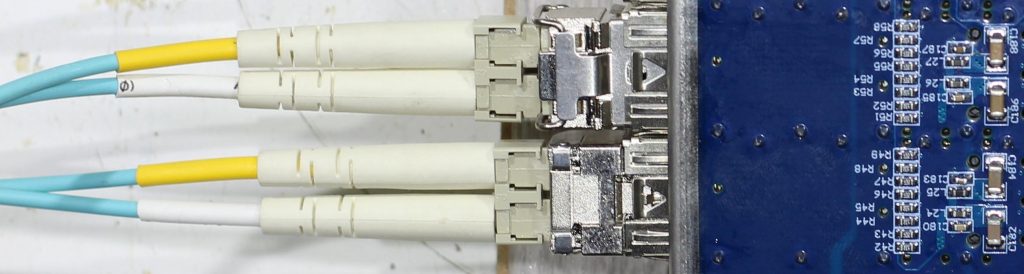

Еще проверил работоспособность IBERT через установленные оптические приемо-передатчики SFP+.

Не забывайте делать бэкап. До новых встреч!

PS. Все публикации этой серии доступны по метке «SATA».