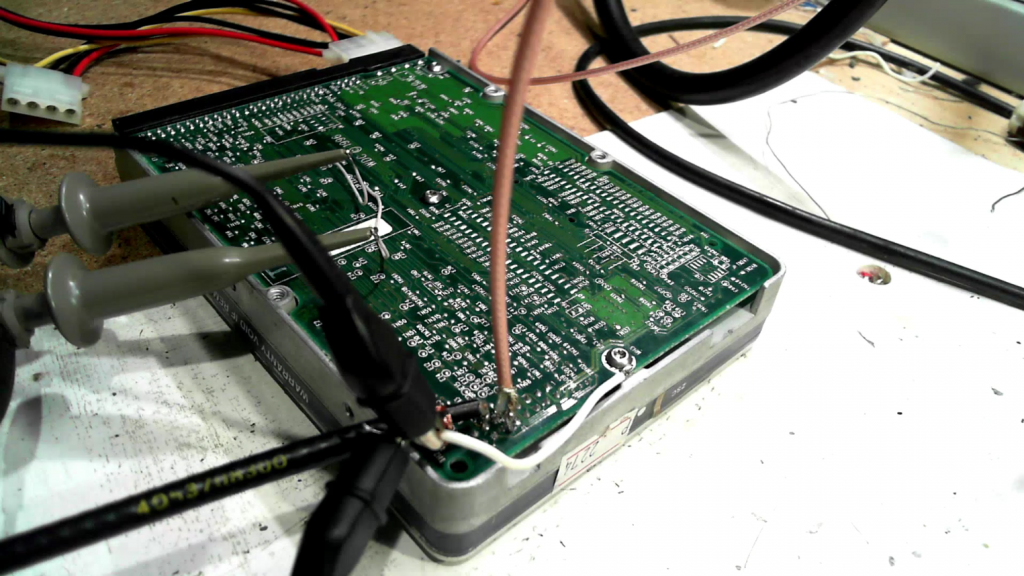

В ролике представлен эксперимент по блокировке записи через установку выключателя на цифровом сигнале перевода предусилителя магнитных головок с режима чтения в режим записи.

В ролике представлена серия экспериментов по изучению сигнала с головки чтения

у старых дисков Western Digital 96 года и Fujitsu 94 и 97 годов при помощи SDR приемника, цифрового осциллографа и программы SDR Uno.

https://youtu.be/BnfZIGPiN5I

В ролике представлена серия экспериментов по изучению сигнала с головки чтения у старых дисков семейства WD31600 при помощи SDR-приемника, цифрового осциллографа и программы SDR Uno.

https://www.youtube.com/watch?v=bzuH6xPsxdw

Продолжаем исследование из цикла изобретения жесткого диска. За время с прошлой публикации было несколько попыток разобраться в коде подопытного кролика в тему стартовой инициализации. Оказалось, что подробно изучить код написанный на чистом ассемблере и отсутствии описания для двух важных микросхем (WD61C28C и WD61C13A) на практике не получилось. Поэтому, было принято решение пойти вобход. А именно, заполучить возможность инструментации кода программы управления диском. Проще говоря, в каких-то местах внедрить свой код, который лампочкой мигает на не использованной ножке процессора или еще что-нибудь. А как такое сделать, если код программы записан в однократном ПЗУ?

В принципе, можно вместо однократной ПЗУ установить совместимую Flash ПЗУ и ее на программаторе переписывать. Но, более продвинутой методикой является реализация эмулятора 16-и битного ПЗУ, что как бы удобнее, но трудно в реализации. Еще хотелось бы изучить HDD других фирм середины 90-х, что и WD21000, например Fujitsu MPA.

На текущий момент придумана схема эмулятора ПЗУ и выложена на гитхаб:

https://github.com/rlabru/HDD_ROM_Emulator

Печатная плата еще в процессе разработки. Собственно, следующее включение по теме, надеюсь, будет по завершению разработки платы.

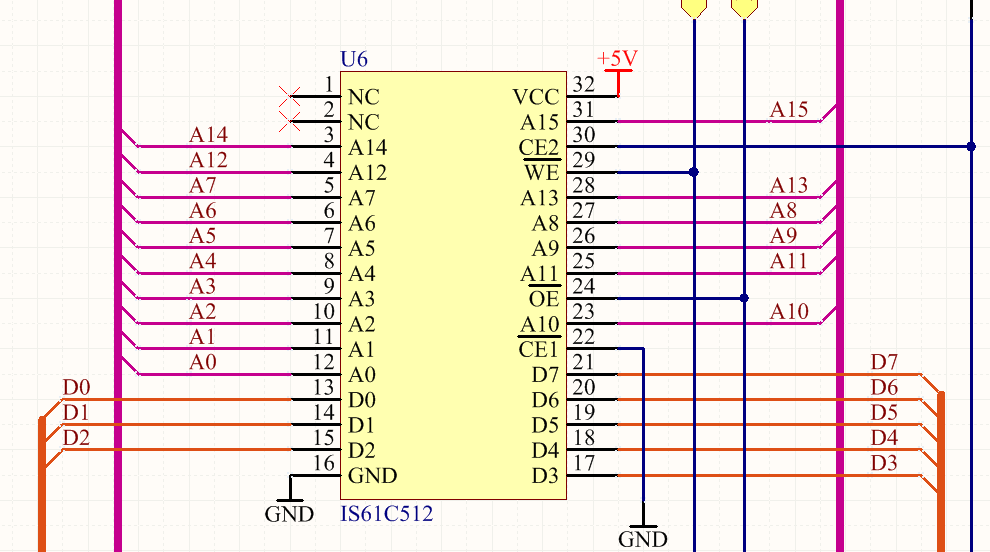

Центром эмулятора являются две микросхемы 8-и битной статической память IS61C512, которые со стороны процессора платы жесткого диска видны как 16-и битное ПЗУ, а со стороны персонального компьютера видна как ОЗУ через плату STM32 NUCLEO64.

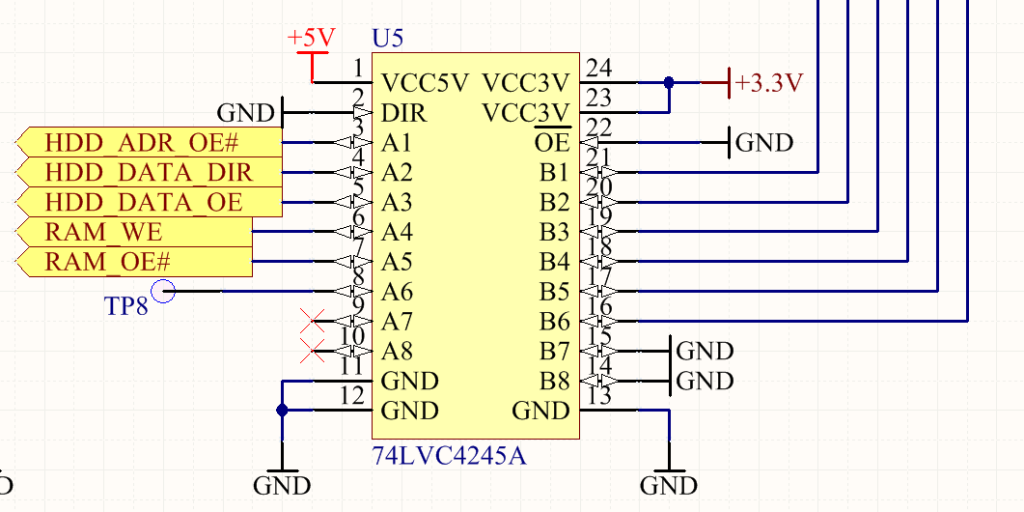

Переход с уровней 3.3 вольта платы NUCLEO64 на логические уровни 5 вольт памяти и платы HDD выполнен на микросхеме 74LVC4245.

Не забывайте делать бэкап. До новых встреч.

ЗЫ. В теории, производительности NUCLEO64 хватит, чтобы наблюдать, по каким адресам «ходит» программа процессора HDD.

ЗЫ. ЗЫ. Обновлена схема WD21000 на гитхабе https://github.com/rlabru/WD21000/tree/master/sch.

В процессе доработки схемы была найдена библиотека со старыми (эпохи до изобретения даташитов в pdf-формате) каталогами микросхем для жестких дисков:

http://www.bitsavers.org/components

Выделил описание микросхемы VM71110 и загрузил на гитхаб, как дополнение к схеме WD21000.

Различные аппаратно-программные комплексы восстановления информации (например, PC-3000 HDD) дают возможность читать и записывать данные из/в служебную служебную зону жесткого диска, но где она физически находится? Попробуем провести эксперимент по определению положения этой зоны на магнитной поверхности.

Видео начинается с фразы «- Попробуем с ним такой же опыт проделать.» так как до этого WD 3.5 дюйма был еще диск WD 2.5 дюйма с которым такой опыт не получился так как диск отказался без крышки запускаться. Попробуем изготовить крышку с отверстием, чтобы крышка была установлена и было видно позицию головок.

В разных частях города Ростова-на-Дону можно наблюдать странные украшения домов — коричневые восьмерки. Оказывается, это телевизионные антенны за которыми закрепилось название «Антенна- чебурашка».

Мало кто знает, что этот артефакт заката советской эпохи сделан из двух «блинов» от прадедушки современных жестких дисков — НЖМД для ЭВМ третьего поколения серии СМ. Коричневый оттенок вызван магнитным слоем, содержащим оксид железа. В то время, как современные диски используют покрытие на основе хрома.

В коллекции раритетных носителей в офисе R.LAB есть один такой носитель. Вот он:

Этот «ИЗОТ» копия 14-ти дюймового диска объемом где-то 3 Мбайта от «винчестера» IBM 3340. Бурная эволюция систем хранения данных сделала их не нужными за несколько лет.

Второе видео из серии реализации проекта подключения жесткого диска или SSD к компьютеру через интерфейс Ethernet. В нем паяем плату переходника от платы Wukong к кабелю жесткого диска.

PS. Все публикации этой серии доступны по метке «SATA».

Первое видео из серии реализации проекта подключения жесткого диска или SSD к компьютеру через интерфейс Ethernet. Для подключения используется FPGA (ПЛИС) фирмы Xilinx из серии Artix-7. Этот проект является продолжением серии публикаций посвященных конструкции SATA интерфейса и его реализации при помощи универсальных приемопередатчиков встроенных в FPGA.

PS. Все публикации этой серии доступны по метке «SATA».