После перерыва в год, мы выпускаем новую публикацию по исследованию WD21000. Такая длительная пауза была обусловлена постепенным усилением технологической базы всех проводимых исследований, как программных, так и аппаратных. Итак, после того, как уровень поднят, можно пользоваться наработками.

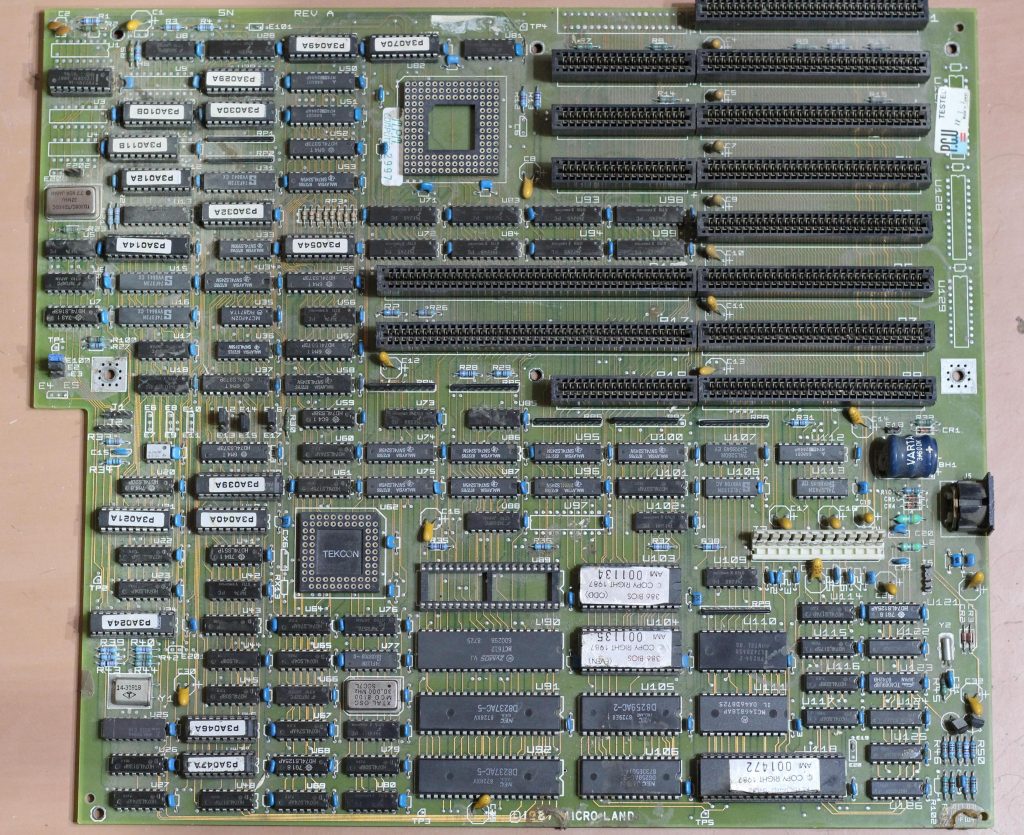

Начнем с того, что обновлена принципиальная схема. Уточнено подключение процессора 80С196.

А еще вкусного в этом посте то, что он сопровождается ассемблер-листингом из IDA базы на github.

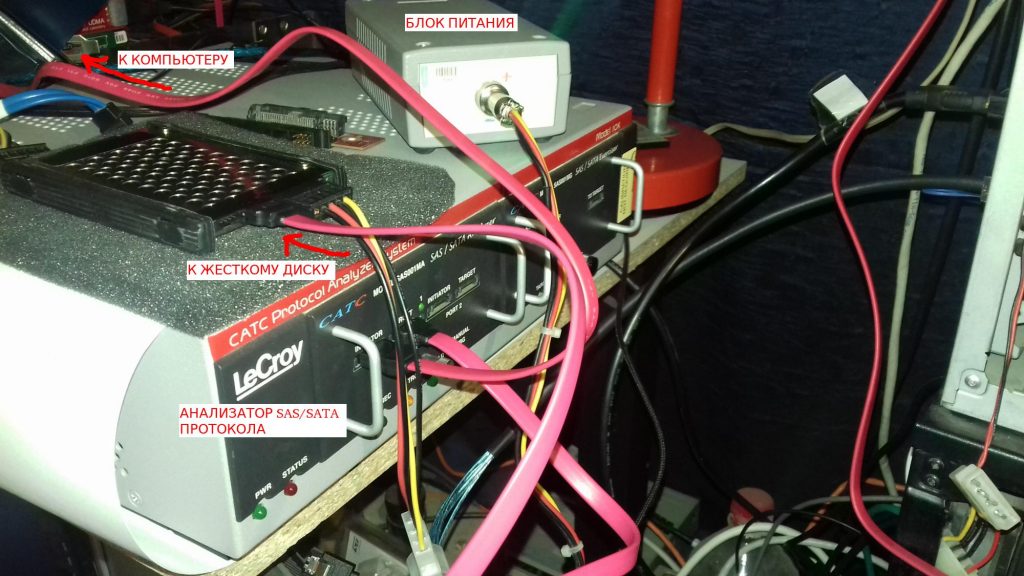

Итак, пришло время задействовать анализатор. Подключение к шине процессора рассматривалось тут (часть 16).

Теперь, хорошо бы понять, как идет управление шпиндельным двигателем, а именно: разгон, стабилизация скорости и торможение. Плюс еще в микросхеме WD61C13A находится синтезатор частоты. Возможно, он как-то тоже управляется. Полученные знания попробую протестировать на макете — при помощи подключенного к этой микросхеме процессора STM32 (Часть 15)

Еще важный момент. У автора этого опуса нет глубоких знаний ассемблера процессора 80С196, так как он никогда не писал на нем программы и не отлаживал их. Нет коллекции библиотек и исходников для него, чтобы что-то посмотреть по аналогии. Автор знакомится с героем своего повествования по мере написания этого текста. Поэтому, набираться опыта и знаний нужно по схеме: смотрим анализатором, как работает и ищем это в коде. Находим — хорошо! Пытаемся понять зачем. А вот если не находим, то отмечаем, что есть какое-то непонимание. Формулируем вопрос и заносим его в список неизвестного.

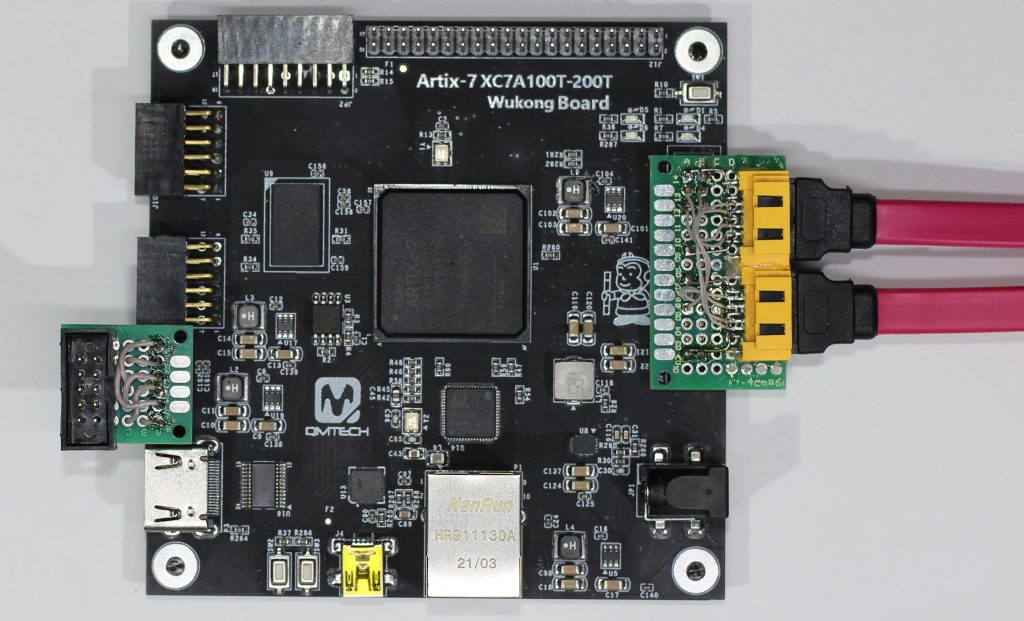

Для решения задачи потребуется прибор, назовем его «счетчик/синхронизатор». Проблема в том, что анализатор ловит случайный пакет по входу синхронизации. Не получается посмотреть, например, первый от включения диска запрос к интересующей микросхеме, второй и так далее.

Чтобы посмотреть номерные обращения нужен счетчик импульсов сигнала «CS3#», который когда досчитает до заданного номера выдаст сигнал синхронизации. А уже от этого сигнала сработает анализатор и запишет кадр.

Проект счетчика/синхронизатора сделан в среде Arduino под плату STM32 Nucleo-64, F091RC.

Исходный код программы на github.

Для того, чтобы среда разработки Arduino могла работать с STM32 нужно поставить соответствующий модуль.

Используется аппаратный таймер в режиме счета импульсов, поступающих на вход «D2».

В процедуре void InputCapture_IT_callback(void) есть условие вида:

« if(isInputCapture >= 9) {», где число 9 задает количество отсчетов до срабатывания выхода «D4».

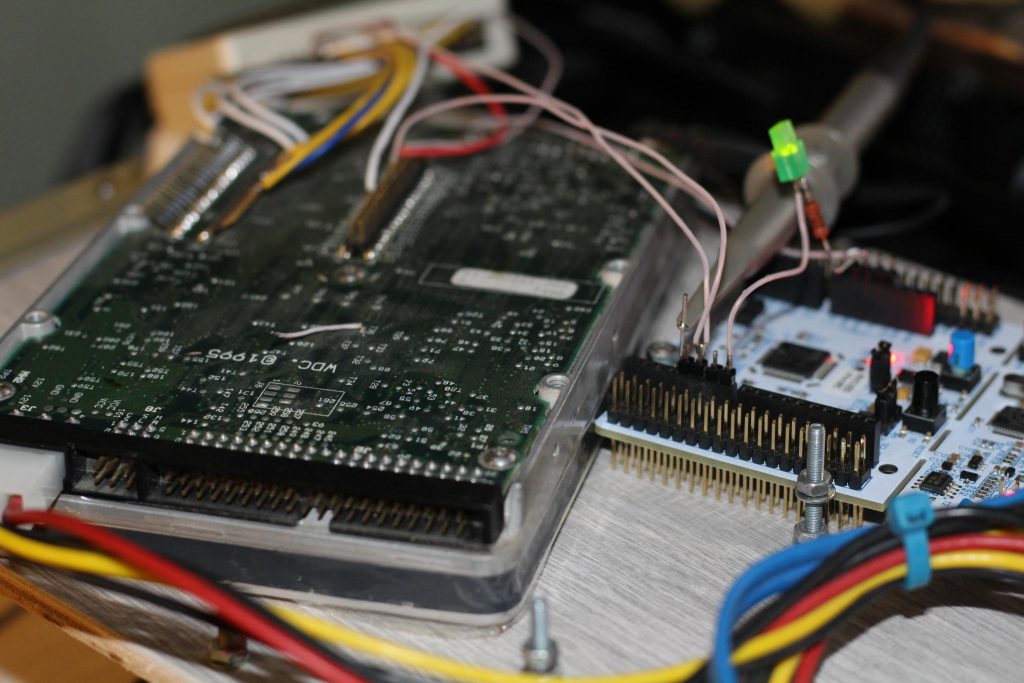

Процесс постановки опыта по записи осциллограммы одного обращения по сигнал CS3#:

1) установить значение условия срабатывания;

2) собрать и загрузить программу в плату;

3) запускать кнопкой RUN/STOP осциллограф в режим ожидания сигнала триггера;

4) подавать питание на жесткий диск.

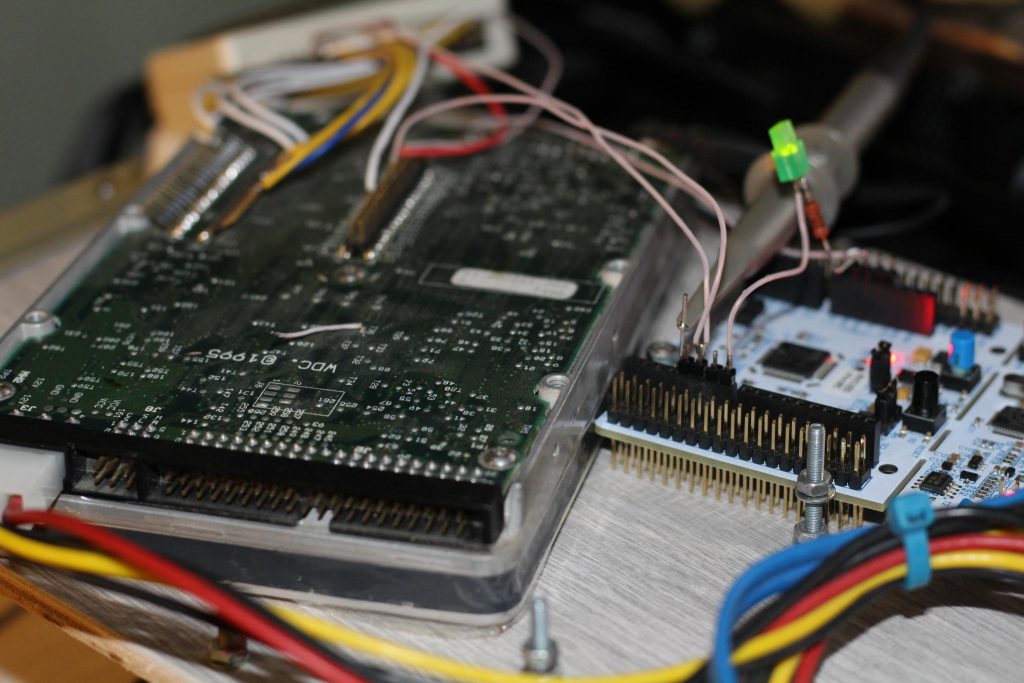

Тестовая установка:

Continue reading →