Доброго дня, дорогие читатели! В этой части разговора про интерфейс SATA рассказ пойдет про набор инструментария, который удалось собрать для детального изучения и реализации контроллера в микросхеме ПЛИС.

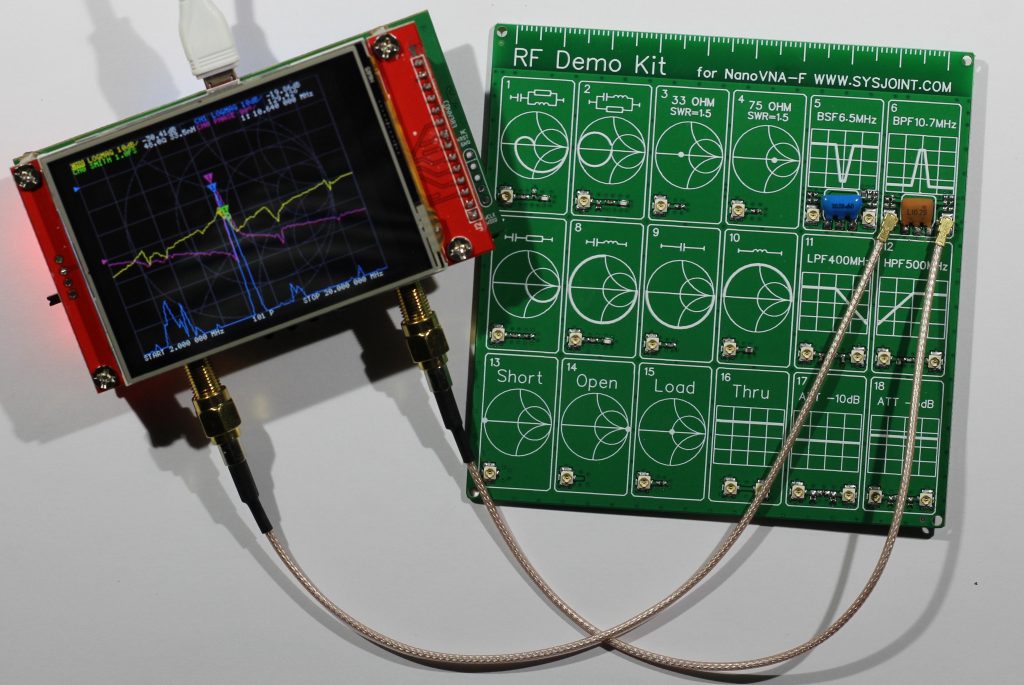

Для исследования поведения SATA разъемов и кабелей в диапазоне СВЧ купил вот такой векторный анализатор:

Однако задействовать я его пока не могу, так как он имеет коаксиальный одно проводной выход и вход, а в SATA используется двух проводный.

Следующим приобретением стала книга: «Цифровой синтез: Практический курс» с курсом по языку описания микросхем ПЛИС «Verilog».

Дело в том, что все исходные коды, доступные на гитхабе почему-то именно на этом языке, в применении которого у автора практического опыта нет (есть опыт на языке VHDL). Надеюсь, это учебное пособие даст возможность освоится с исходными кодами SATA контроллеров. С этим пособием еще трудность в том, что примеры там под микросхемы ПЛИС фирмы Altera (теперь это снова Intel) и, придется, адаптировать их под пакет ПО Xilinx.

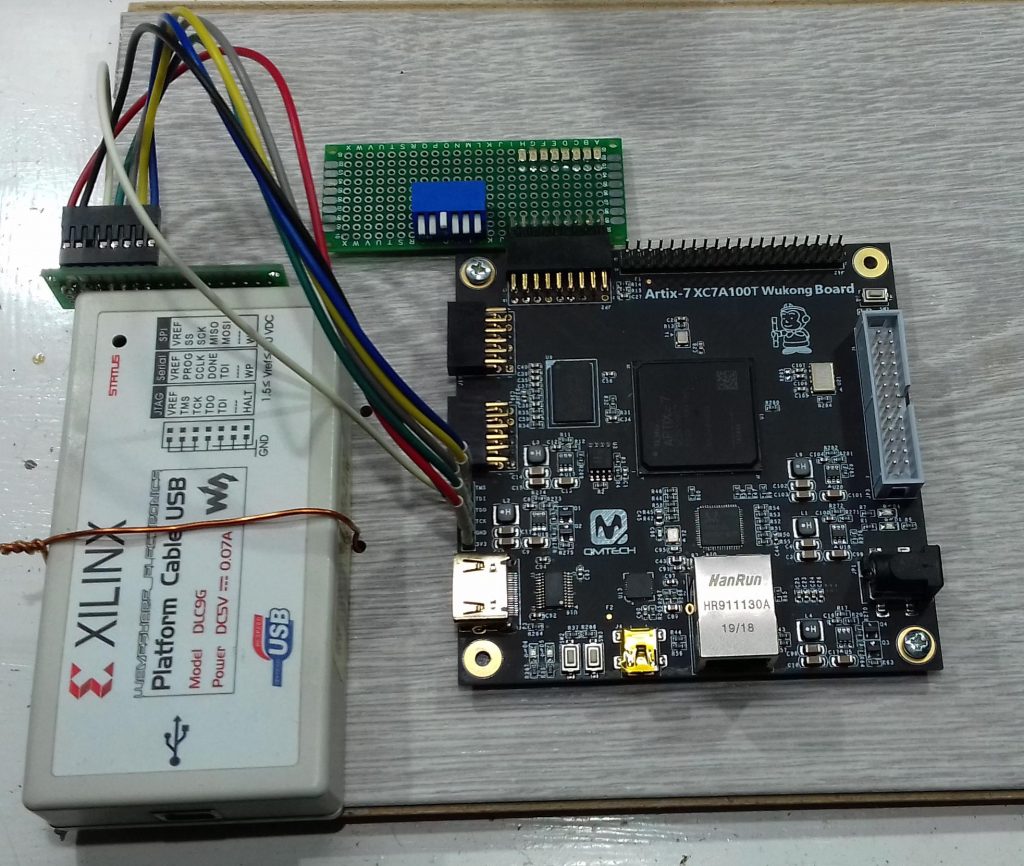

Далее, идет уже упоминавшаяся в первой части плата Wukong:

К ней подключены дополнительные переключатели и светодиоды для освоения примеров Verilog из пособия. Скоростные интерфейсы GTP для реализации SATA выведены в серый разъем, который как бы ни разу не высокочастотный, но работать на 3 гигабита, думаю, будет.

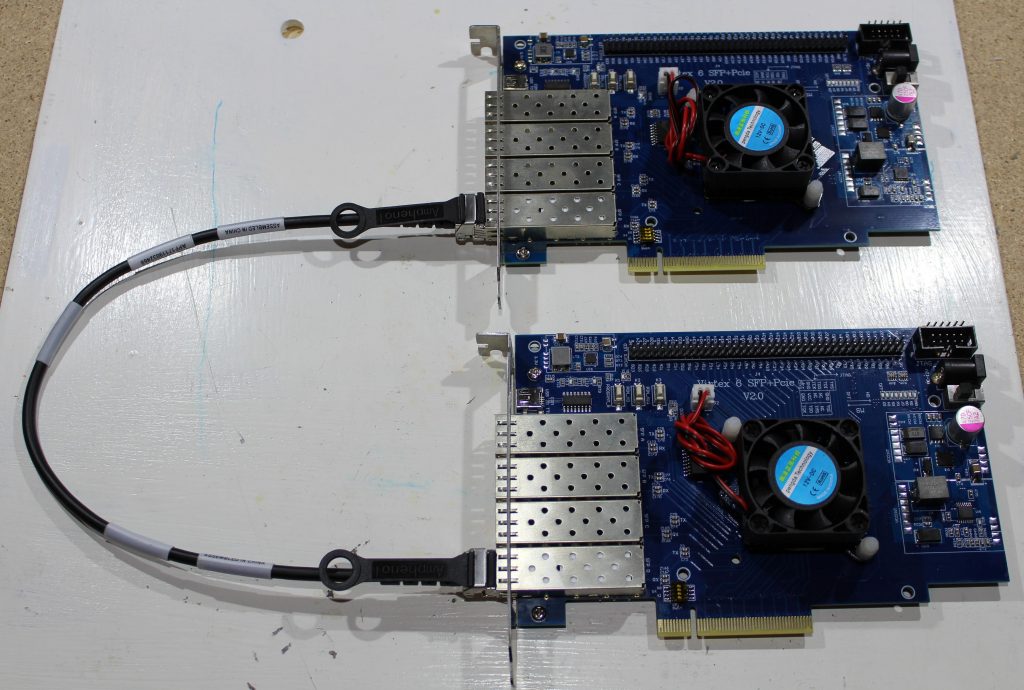

С парой китайских «no name» Virtex6 плат читатель уже познакомился в предыдущих двух частях:

Ну и качестве вишенки на торте выступает анализатор интерфейсов SAS и SATA фирмы LeCroy (CATC Protocol Analyzer System, SAS001MA SAS/SATA):

Коробочка справа с надписью «LeCroy» — это именно он. Через него подключен жесткий диск WD.

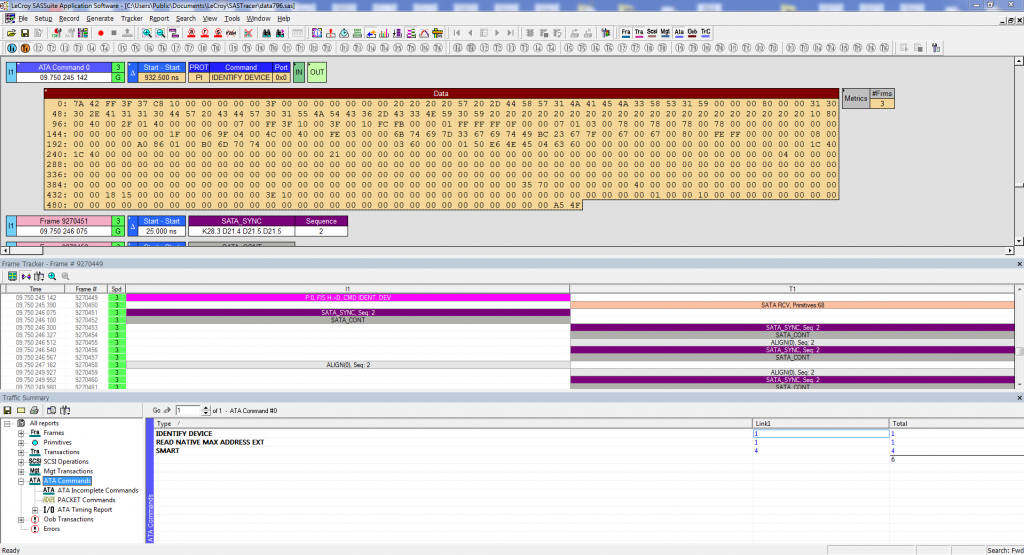

Анализатор показывает как самый низкий уровень интерфейса, так и уровень ATA команд. Вот как выглядит в нем транзакция с командой ATA «идентификация диска» (в терминологии PC-3000 — паспорт диска):

Думаю, этот наборчик инструментария позволит освоить построение программ для ПЛИС контроллеров SATA, а может, даже SAS.

Не забывайте делать бэкап. До новых встреч!

PS. Все публикации этой серии доступны по метке «SATA».

Спасибо за продолжение истории

Вот эту книжку возьмите: https://www.ozon.ru/product/osnovy-yazyka-proektirovaniya-tsifrovoy-apparatury-verilog-solovev-valeriy-vasilevich-264572310/

Отличный справочник непосредственно по языку Verilog, без нудной тягомотины для начинающих, повторяющейся в различных вариациях из книжки в книжку. Очень рекомендую.